# The Swiss Army Knife for HDL Design Engineers

HDL Companion is like the Swiss Army Knife. It provides the HDL Design Engineer with 1001 different features like: Syntax checking, Design Exploration & Navigation, Signal Tracing, Linting, HDL Sensitive Editor, Global Search and Replace, HTML Generator, Source Revision Control and an EDA Tools configurator. It is easy to use, affordable and should be present in each designers toolbox.

In the past a designer had to use a simple text editor and Unix like 'grep' commands to find his way through many lines of HDL code or use a costly simulator license to understand the design structure. With HDL Companion a designer can drag and drop design files or directories into the file view and a complete design decomposition is performed in seconds, offering information regarding numerous aspects of the design.

# **HDL Companion**

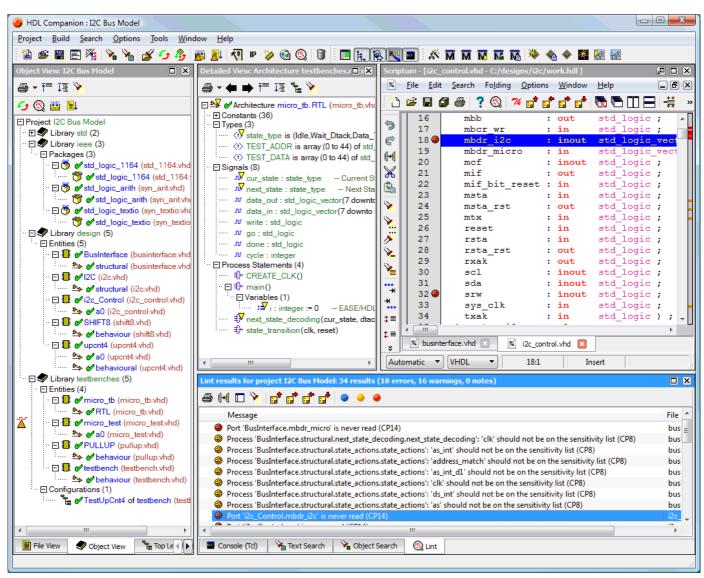

HDL Companion consists of four windows including a command console. Together they offer a complete overview of your design, from library level down to the details of your HDL source code. Each window can be enabled and disabled separately so you can easily configure the tool to show you exactly the information you are focusing on. HDL Companion is equipped with both fuzzy and fully compliant VHDL and Verilog parsers, freeing you from the burden of determining file dependencies while offering you full syntax

checking. Just drag & drop your design folder in HDL Companion and get started.

### **Global Window**

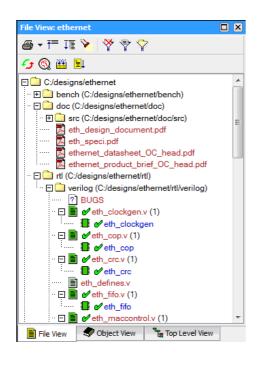

The Global Window is separated into three tab pages offering you a file view, a library / object view and a hierarchical design view. The file view shows you the files present in your design in a browser like manner while also presenting the main design objects contained in each file. You can select any object to either edit it in the integrated HDL Editor (or your preferred editor) or have a more detailed description in the Detailed Window. The file view is not limited to HDL files, but shows all files in your project, providing easy access to all your design data, like PDF and other documents. It is also the place to perform version management actions when a version management system is enabled. File view filters allow you to focus on what you want to see. The object view shows all objects in the design (entities,

architectures, configurations, modules, etc.) organized by HDL library. The hierarchical view shows the hierarchy of the selected design unit. The views are driven by fuzzy VHDL and Verilog parsers. These parsers take care of all the tedious work of placing objects in libraries and determine the correct file compilation order. They also allow you to work with incomplete or erroneous designs. All views are related and allow drag and drop for easy navigation through your project. A tooltip is available which shows you a (syntax directed and scrollable) view of the file contents without opening it.

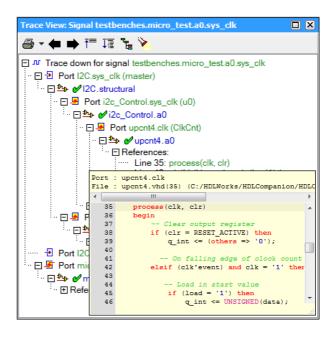

#### **Detailed Window**

The Detailed Window offers you an in-depth view of the structure or hierarchy of a selected HDL object. For an entity or module the list of parameters, ports and architectures is shown, as well as the places where the entity or module is instantiated. This gives you detailed information about where and how signals are used throughout the whole hierarchy of your design. All labels in the tree view are click-able, providing easy access to the source code or other detailed view objects. The Detailed Window is also used to show the trace results of a port or signal. A trace shows how a signal is used through the hierarchy.

### **HDL Editor**

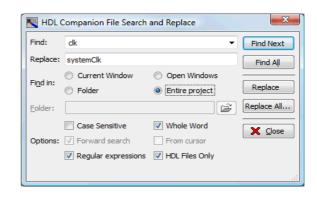

The HDL Editor offers a fully featured language sensitive text editor with a multiple document interface. You can avoid typing errors and improve your productivity by using language templates, identifier repeat and one-touch line and column manipulation. Syntax highlighting keeps your text highly readable and well structured. Functions like 'Search and Replace', 'Copy Entity', 'Copy Instance' and 'Create Testbench' help you to speed-up development tasks. The marker system allows you to drop

markers for fast navigation between various file and text positions. Syntax errors or warnings are shown by coloured dots at the beginning of a line. An overview of all reported issues is shown at the right side of each edit window. Tight integration with the data model allows you to directly jump to object definitions and their use. If you want to use your own favourite text editor, you can configure HDL Companion to use the integrated editor for viewing only.

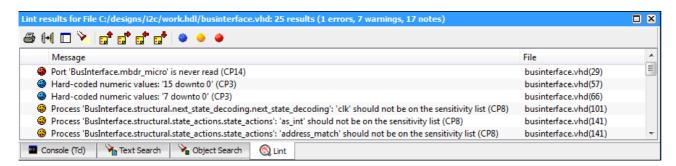

## Linting

Linting is an additional verification effort to find potential design problems (like range mismatches in assignments of vectors, or read-only signals) and optimize the design by identifying unused signals and definitions. HDL Companion also supports a number of the DO 254 guidelines which helps you to improve the design quality. Many lint checks are available, including the following:

| DO 254 Coding Practice:            | Miscellaneous:                                      |  |

|------------------------------------|-----------------------------------------------------|--|

| Avoid duplicate signal assignments | Avoid processes with multiple clocks                |  |

| Avoid hard-coded numeric values    | Avoid latches                                       |  |

| Avoid mismatching ranges           | Avoid positional port map in instantiations         |  |

| Ensure complete sensitivity list   | Avoid reset with different value than initial value |  |

| Avoid unused declarations          | Avoid non standard clock expressions                |  |

The severity level can be set for each check separately or the check can be disabled altogether. Errors, warnings and notes are reported in the verification pane. The messages are hot-linked to the text editor so you can quickly navigate to the offending code.

# **Naming Conventions**

The name convention checking allow you to check any name conventions you specify using regular expressions.

## **TCL** integration

The console window also functions as a TCL interpreter, allowing you to execute any TCL or shell command. The TCL interface offers access to HDL Companion's internal data structures, allowing you to write your own TCL scripts to generate reports, perform specific checks or add your own functionality.

### **HTML**

The HTML documentation function allows you to export the HDL Companion views into HTML documents with the same cross reference links as in HDL Companion. HTML files are created for each HDL file with syntax highlighting and links to units, signals and types. Any view can be printed or placed on the clipboard for documentation purposes.

## **Design Flow**

The tool flow wizard allows you to configure a complete flow of other tools (like simulation, synthesis and FPGA place and route) you want to use in your project. After running the wizard, buttons are present in the toolbar to start your tools. In combination with the top-level marker HDL Companion can compile the HDL files with the selected simulator or generate synthesis scripts for the synthesis tool. HDL Companion projects can also created using FPGA Vendor projects files from Altera, Lattice and Xilinx.

| Features and benefits               |                                                                    |  |  |

|-------------------------------------|--------------------------------------------------------------------|--|--|

| VHDL, Verilog and mixed language    | <ul> <li>Up and running with your design in minutes</li> </ul>     |  |  |

| Syntax checking                     | Design metrics                                                     |  |  |

| Works on incomplete designs         | <ul> <li>Quickly navigate through your design</li> </ul>           |  |  |

| File / Library / Hierarchical views | <ul> <li>Extensive search functionality</li> </ul>                 |  |  |

| Distributed directories             | <ul> <li>Signal tracing through the whole hierarchy</li> </ul>     |  |  |

| Fits in any design flow             | <ul> <li>Includes miscellaneous files (Word, PDF, etc.)</li> </ul> |  |  |

| Language Support                                                                                                   | Operating Systems                                                                          | License Configuration                         |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------|

| <ul> <li>VHDL 87, VHDL 93,<br/>VHDL 2002, VHDL 2008</li> <li>Verilog 95, Verilog 2001,<br/>Verilog 2005</li> </ul> | <ul> <li>Windows Vista / 7 / 8</li> <li>Linux (x86 PC, any recent distribution)</li> </ul> | Node locked     Floating     FlexLM protected |

HDL Works B.V. Maxwellstraat 19 P.O. Box 620, 6710 BP Ede The Netherlands

Phone: +31 (0)318 642 022 E-mail: info@hdlworks.com http://www.hdlworks.com